By GO SEMI & BEYOND Staff

The rapid proliferation of generative pre-trained transformers based on large language models (LLMs) is driving growth in the market for chips that can run the LLMs and other artificial intelligence (AI) and machine learning (ML) applications. Several types of chips hold promise for accelerating AI computing. Graphical processing units (GPUs) have proven to be capable solutions for the server/cloud environment, although work is underway on dedicated AI chips that could offer higher efficiencies. Edge applications will require lower-power devices, such as neuromorphic chips, which mimic neural network behavior. Personal computers are also gaining AI capabilities as chipsets appear to accelerate AI program execution without requiring cloud resources.

AI chip market

Research firms see a booming market for these AI-capable chips, although the exact numbers remain unclear because of the variety of classes of the devices. Mordor Intelligence forecasts that the market for GPUs will grow from about $65.3 billion in 2024 to $274.2 billion in 2029, driven by both graphics and AI applications. For its part, Gartner forecasts that worldwide AI chip revenue will increase from $53.4 billion in 2023 to $119.4 billion in 2027. Future Market Insights takes a longer look and forecasts that the AI chipset market will increase from $27.6 billion in 2024 to $287 billion in 2034—a CAGR of 26.4%. Deloitte puts the market for specialized chips optimized for generative AI at more than $50 billion in 2024, representing two-thirds of all AI chip sales during the year.Market.us surveys the complete global AI chip market, including GPUs, and estimates it is growing at a CAGR of 31.2% and reaching $341 billion in 2033.

Finally, as AI comes to the home and business desktop, personal computers will increasingly include dedicated chipsets that can accelerate AI computing, executing AI applications without requiring cloud connectivity. Canalys predicts that 60% of PCs shipped in 2027 will be “AI-capable,” up from 10% in 2023.

AI chip characteristics and test challenges

The diverse classes of chips applicable to AI computing present unique test challenges, but several are common to most of them. For example, increases in device complexity are causing an explosion in scan-pattern depth, with pattern depths moving from what used to be a doubling every three years toward increasing tenfold every three years. Such growth necessitates new ATE technologies as well as the use of more efficient test data distribution schemes inside the device for higher throughput and parallel test of multiple cores.

The test flow for AI-enabled chips remains similar to that for traditional devices. Key stages in the flow include post-silicon validation, wafer acceptance test, wafer sort, final test, burn-in, and system-level test (SLT).

However, test-flow stages must become dynamically adaptable with real-time decision-making to minimize the cost of the test (COT), maximize yield, and facilitate dynamic failure analysis. In addition, test must occur in accordance with specific application requirements because scan testing exhaustively is becoming too expensive. Consequently, functional test content is moving forward in the flow in order to focus the valuable test time on the best parts. Additionally, binning must move from the performance-based approach of traditional test to an application-based approach that facilitates die matching (harvesting and smart pairing).

The dynamically adaptable test flow requires the seamless sharing of data across multiple test insertions and throughout the manufacturing process. It is also necessary to correlate behavior across insertions—to predict from a wafer-test result what will happen at future insertions, for example, and to identify defects before packaging.

Products and Services for AI chip test

Advantest offers a full lineup of test solutions for AI-capable chips that perform high-quality, cost-effective tests at high throughput. These platforms feature a module-based architecture that enables flexible reconfiguration of test modules to meet the ever-expanding list of test methods and applications.

In addition to the test platforms, Advantest offers associated equipment ranging from die-level handlers and thermal controllers to test-interface boards. In the handler and thermal-control category, Advantest provides the HA1200 die-level handler to support the test of singulated or partially assembled die. Equipped with Advantest’s ATC advanced thermal control option, the HA1200 enables known-good-die (KGD) testing of high-power, high-performance AI-capable devices within a thermal environment similar to their final assembly location. Testing in this fashion helps ensure true KGD for parts shipped in die form, chiplets, and large AI components that use back-side power delivery.

The company also offers an ATC 2kW solution for its M487x handler series to provide advanced thermal control at final test. Rounding out the hardware offerings from Advantest are high-performance DUT boards, test sockets, and thermal-control units, which accommodate very large form factor devices, including ones with coaxial electrical interfaces.

Advantest SLT and burn-in systems also provide a variety of thermal options to accommodate these large packages and high-power devices. These SLT thermal solutions include but are not limited to, active cooling and heating with fast dynamic response to maintain setpoints without overheating the DUT.

To handle the compute-intensive aspects of chip production and test, Advantest offers Advantest Cloud Services (ACS), which provide data management and analytics to pull together data from across the value chain. Included in ACS is Advantest’s ACS Real-Time Data Infrastructure (ACS RTDI) platform, which collects, analyzes, stores, and monitors semiconductor test data in a True Zero Trust security environment to enable customers to convert insights into actionable steps while protecting IP. In addition, the company’s ACS Edge platform can work in conjunction with Advantest’s platforms to handle computationally intensive workloads locally without loading down the test program or requiring cloud intervention. This addresses the growing industry need to run advanced, complex analytics at multiple test insertions while achieving very low and predictable latency.

Scan test

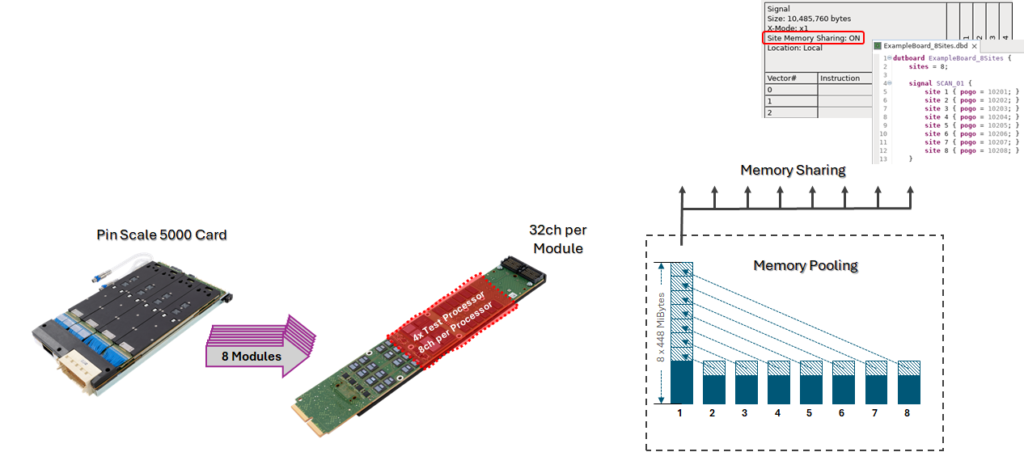

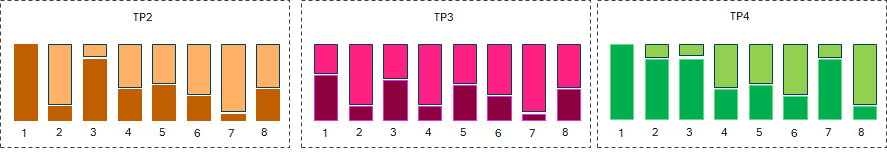

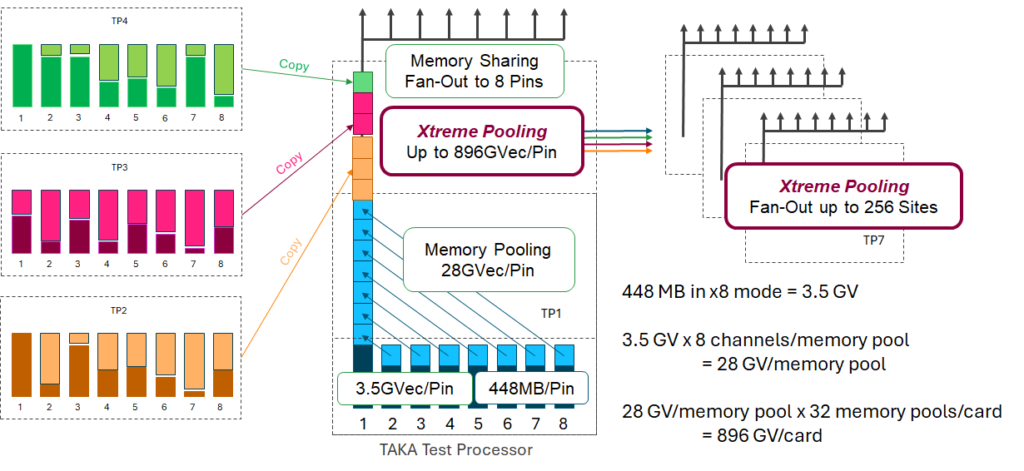

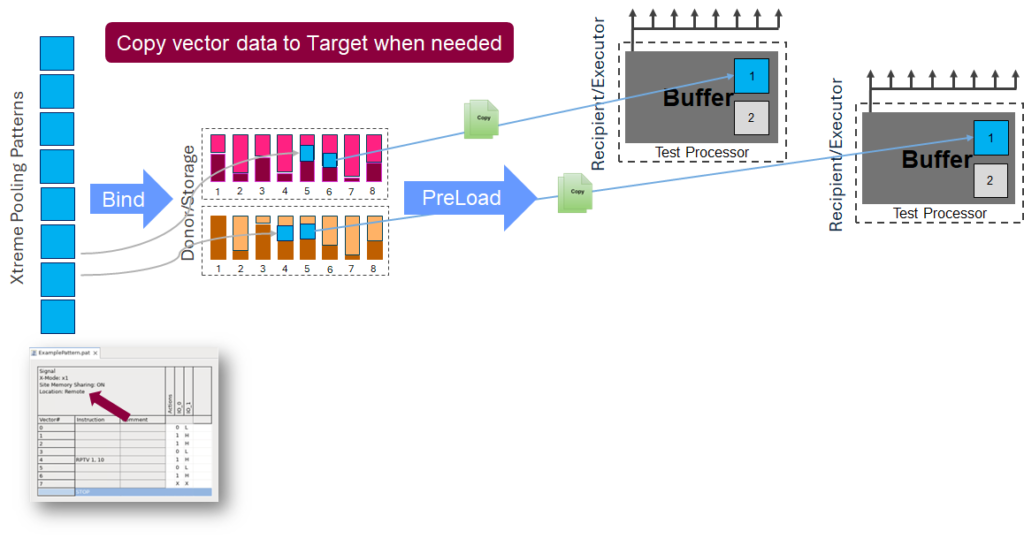

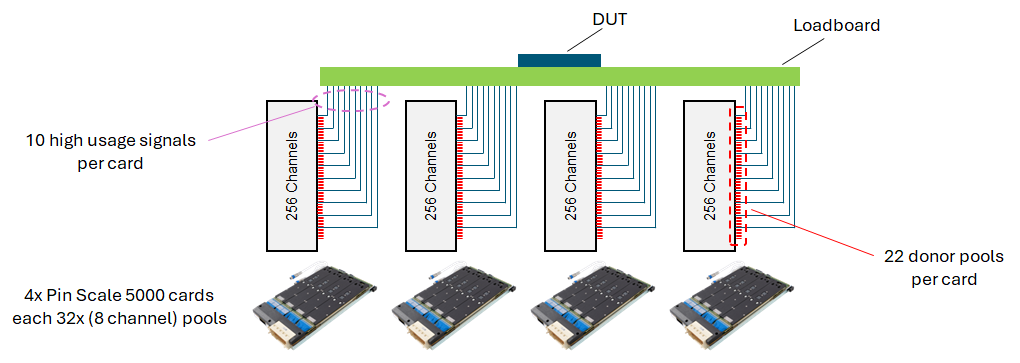

For scan test, the tester must efficiently move scan data in and out of the DUT. Test patterns must be deployed at the KGD testing step as well as at the final test of the complete heterogeneously integrated device. To accommodate tenfold pattern depth increases, testers require much greater memory depth. To meet this requirement, Advantest offers the Pin Scale 5000, which has multiple giga vectors per pin at up to 5 Gb/s.

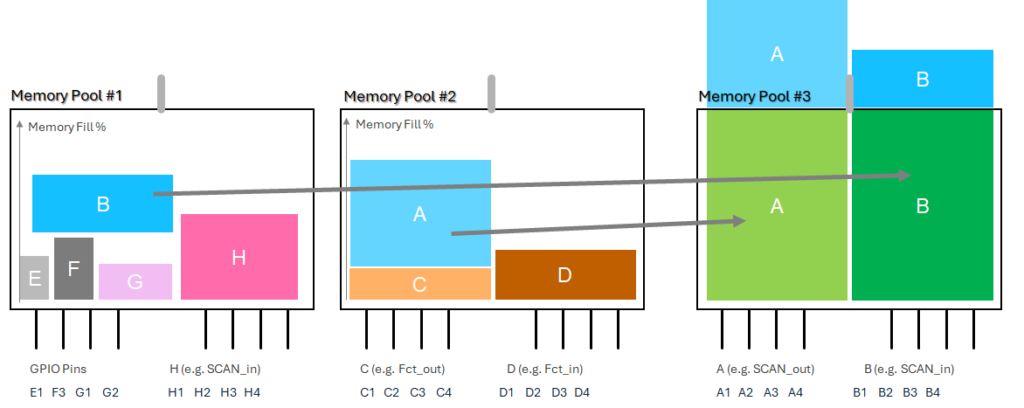

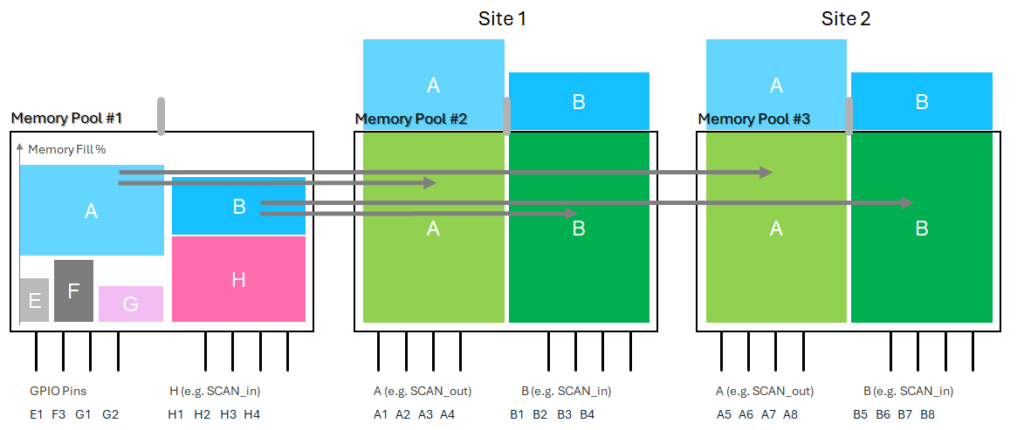

Compression and memory pooling can scale this capacity significantly, either per pin or across multiple pins.

Some devices already require terabits of scan-pattern test data. Depending on the scan architecture, the available I/O speed, and the number of I/Os available for scan test, it can take many minutes to run a comprehensive scan pattern set on a very large device, which leads to high test cost and low throughput. As an alternative, a device’s native PCIe interface running at 16 Gb/s (with future versions moving to 32 Gb/s and 64 Gb/s) can also transport scan test data if the device-internal DFT supports it. To enable the use of PCIe or other serial interfaces, Advantest offers the Link Scale digital channel cards for the V93000 platform that enable software-based functional testing and PCIe (or USB) scan testing. Coupled with the latest generation of on-die scan data distribution networks, Link Scale can provide an order of magnitude faster pattern execution compared to traditional approaches. Alternatively, Advantest’s SLT and burn-in systems can utilize the same device-internal DFT and our controllers’ PCIe or USB interfaces to execute the same SCAN patterns that were generated for use on the V93000 Link Scale solutions. SLT and burn-in systems typically are less expensive per test site but run for much longer durations.

Power requirements

The tester must also deliver sufficient power to the DUT while preventing overheating. Some devices are already drawing over 1,500 A, with future plans for 2,500 A and more, so controllability of the power resources is critical, requiring precise regulation, fast clamping capability, and in-line monitoring of contact resistance. In addition, supply voltages are being reduced from 1 V down to 750 mV, 600 mV, and even 500 mV. Each voltage drop requires higher accuracy. Power supplies must also be simple and flexible, enabling system configuration without buying more resources than needed.

To meet test power-supply requirements, Advantest now offers the XHC32 high current power supply for the V93000, which delivers up to 640 A per card and is an ideal complement to the widely used XPS256 universal power supply. Both cards feature digital regulation, fast clamp response, extended profiling capabilities, and state-of-the-art protection features for probe cards and sockets. In combination, they serve the needs of power-hungry performance digital devices for years to come. For our SLT and burn-in test cells, a similar power is available to each DUT in a highly parallel environment.

Scan and power requirements, taken together, have implications for multisite test as DUT pin counts vary. Scan port width may vary from tens of pins to hundreds of pins, and power requirements are constantly increasing. Bandwidth requirements for test data transmission greatly increase in parallel. Very large devices combining multiple dies in one package are also becoming increasingly prominent, especially in the HPC segment. As these chips have large numbers of I/Os, real estate on existing DUT boards is not always sufficient to accommodate all the external components required for test, especially in multi-site setups. The new DUT interface DUO available on the V93000 helps with this by significantly increasing the available space for large DUT interface boards while maintaining compatibility with existing DUT boards.

Boot-up and system-like test

In addition to scan and functional test, the tester must confirm that the chip meets its intended requirements for AI applications, such as object recognition. This level of testing requires DUT boot-up and execution of software on the DUT during the test insertion, which is typically performed during SLT. Interfaces such as PCIe are suitable not only for scan but also for the exchange of large amounts of data that would enable a chip to run a convolutional neural network or similar application. Boot-up sequences and interfaces such as PCIe can present fundamental problems that, if found only at SLT, impose significant time and cost issues for parts destined for heterogeneous integration.

To avoid these issues and to shift the boot-up test left, Advantest offers system-like test™ technology, which can help shift boot and other SLT content to wafer probe. Link Scale can alternatively act as a source of data, providing a data array for an AI processor.

Machine-learning driven test

And finally, Advantest is also leveraging ML to test ML-capable devices. The company has demonstrated test time and cost reduction using intelligent prediction from ML models. Customers with strong in-house data-science teams can develop similar models and run them on Advantest’s infrastructure. Advantest is continuously investigating AI-based methodologies to support its customers.

Table 1. Advantest products and technologies for AI-enabled chip test

Conclusion

As we step into the AI-driven future, the complexity of testing AI-enabled chips intensifies, marked by significant increases in test-data volumes and challenges related to heterogeneous packages with restricted access. Advantest is at the forefront of addressing these challenges with its robust portfolio (Table 1) of cutting-edge test hardware and sophisticated cloud-based services. Leading this transformative era, Advantest ensures its customers consistently remain on the leading edge of technology. By not only meeting today’s stringent demands for AI chip testing but also anticipating future needs, Advantest positions its partners for success. As AI reshapes industries and expands the horizons of possibility, facing the future of technology together with Advantest ensures your technology is always ahead and fully equipped to leverage the immense potential of the AI era.

Read More