Interview with Oded Olansky, VOICE 2025 Chairperson

Advantest’s VOICE 2025 Developer Conference will take place May 12-14 at the AT&T Conference Center in Austin, Texas. To learn what VOICE 2025 holds in store for attendees, we interviewed this year’s general chairperson, Oded Olansky, WCS RF Products Si Test Architect and WCS Haifa Wireless Test Engineering Manager, Intel.

By GO SEMI & Beyond Staff

Q. With VOICE 2025 taking place in Austin, how will this year’s location impact the event?

A. Austin is significant to the semiconductor industry. Major companies like Tesla, Amazon, AMD, Microsoft, and NXP have a strong presence in the area, with Texas Instruments located nearby in Dallas. This makes Austin a vibrant hub for industry and innovation, which is why we believe it is the perfect location for VOICE 2025. With our venue situated in the bustling heart of the city, we are excited to host VOICE 2025 in Austin and invite our attendees to enjoy the city’s rich culture.

Q. As the VOICE 2025 chair, what do you hope to see, or what do you hope attendees will gain?

A. For me, the VOICE conference has always represented a unique opportunity to explore emerging technologies and innovative testing methodologies, whether through presentations, kiosks, or invaluable networking opportunities with test engineers from diverse companies and countries. I hope that attendees of this year’s conference will experience the same. Personally, I believe that if, upon returning from the conference, I can apply even one new insight or idea successfully in my work, then the conference has been both successful and worthwhile. I encourage the attendees of VOICE 2025 to set a similar goal for themselves.

Q. I heard that there will be an exceptional number of presentations at this year’s event. What presentation topics and industry trends are you most excited about?

A. Our committee accepted over 100 technical papers this year, with a record line-up of over 130 presenters. These numbers tell us that people are excited about the state of the industry right now and are eager to discuss the latest trends and innovations with their peers.

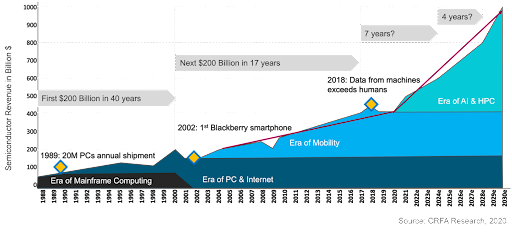

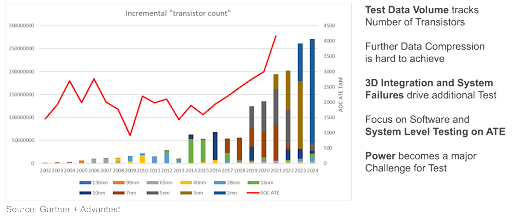

I believe we are currently witnessing a transformative revolution in the field of artificial intelligence, particularly in the area of generative AI. This revolution strongly echoes the impact of the Internet revolution, which began around the time I started my career in test engineering. As such, I am particularly eager to see presentations and engage in discussions surrounding this topic, as it promises to reshape the industry in profound ways.

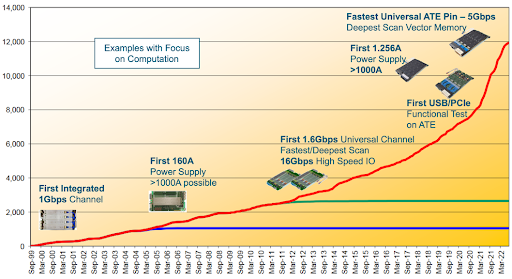

There will also be presentations regarding the new instruments for the V93000 EXA Scale platform that were announced last year, including the DC Scale XHC32 ultra-high-current power supply. Presentations will also feature the new PMUX02 advanced power multiplexer for the V93000, which offers unprecedented capabilities for multi-site testing of power and analog devices, including battery-management systems (BMS), automotive, and power management IC.

Q. What highlights of this year’s event do you recommend attendees not miss?

A. There is plenty to look forward to at VOICE 2025. The conference will kick off on Monday evening with a welcome reception, offering a great opportunity to network with representatives from top semiconductor companies. At the same time, we will host the Technology Kiosk Showcase, featuring exciting displays of cutting-edge innovations that highlight Advantest’s diverse product portfolio.

Tuesday and Wednesday will feature engaging keynotes from semiconductor market analysts and leading professionals. The Partners’ Expo is also open throughout Tuesday and Wednesday, allowing attendees to engage with our technology partners to discuss their latest products and solutions.

Tuesday’s evening event will be hosted at The County Line—a charming lakeside lodge serving classic Texas BBQ and margaritas. The setting provides a relaxed atmosphere that is perfect for mingling with colleagues while enjoying the stunning views of the lake from the venue’s redwood deck. We also have a great lineup of fun Texan-themed activities that everyone can enjoy throughout the evening, including horseshoe tossing and even line dancing lessons. There’s plenty to look forward to, and we invite all attendees to join the fun.

We will wrap up VOICE 2025 on Wednesday afternoon with an awards ceremony honoring the best papers and those receiving honorable mentions. Additionally, we’ll present the Visionary Award, given annually to a customer who has made significant, lasting contributions to VOICE over the years.

Q. Who will be joining us for this year’s keynote addresses?

A. VOICE 2025 will feature three dynamic keynote speakers.

Our first speaker on Tuesday will be John Yi, a Fellow at AMD. With over 30 years of experience, John currently manages a team of test architects responsible for defining new design-for-test (DFT) methods and test solutions with silicon design and product engineering groups that span a wide spectrum of AMD products.

Our next two keynotes will be on Wednesday, starting with John Yick, senior director of product and test engineering at Marvell. John leads Marvell’s product and test engineering teams, driving the production of cutting-edge broadband analog devices such as trans-impedance amplifiers and drivers, as well as silicon photonic integrated circuits (PICs). His expertise spans a wide frequency range, from DC to 110 GHz, all the way to light speed.

Roy Meade, TIE executive director of strategic partnerships at the University of Texas, will present our final keynote on Wednesday. Throughout his career, Roy has exhibited exceptional innovation and leadership in the domains of photonics, packaging, and memory technologies. His contributions to these fields are evidenced by over 120 patents granted by the United States Patent and Trademark Office, encompassing photonics, semiconductor manufacturing, and emerging memory technologies.

As a final note, we would like to thank our VOICE 2025 sponsors for making this year’s event possible—in particular, our headline sponsors, ISE Labs, ASE Group and Alliance ATE Consulting Group. The full list of sponsors can be found here.

To learn more about keynotes, papers, and other details related to VOICE 2025, be sure to keep checking the VOICE website. And don’t forget to register here to reserve your spot!

Read More