Advantest to Exhibit Wide Range of Semiconductor Test Solutions Enabling 5G Connectivity at SEMICON Japan on December 12-14

Advantest Corporation will feature more than a dozen of its advanced test solutions that enable 5G connectivity for such diverse applications as mobile electronics, medical devices, automotive systems, retail business and big data at SEMICON Japan 2018 on December 12-14 at Tokyo Big Sight.

“This year, we are showcasing our range of capabilities in measuring the connected world and everything driven by 5G communications,” said Judy Davies, Advantest’s vice president of global marketing communications. “The product portfolio that we have – and are continuing to develop – is designed to meet the global market’s requirements for 5G in applications from next-gen smart phones to connected cars.”

Product Displays

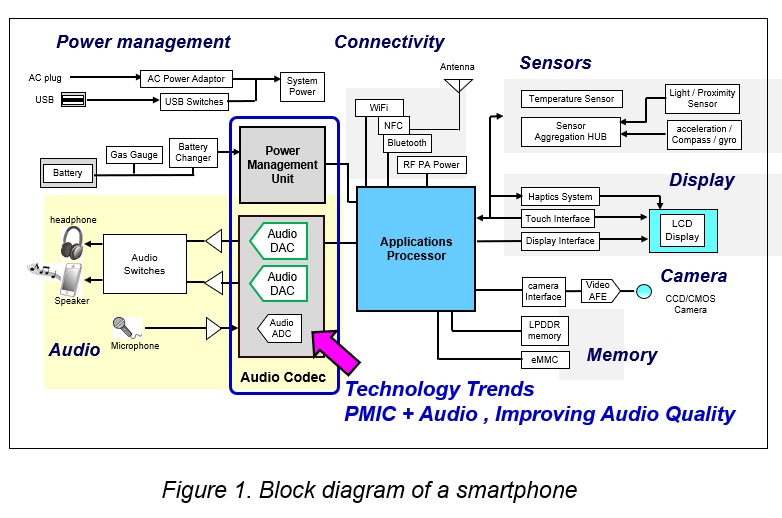

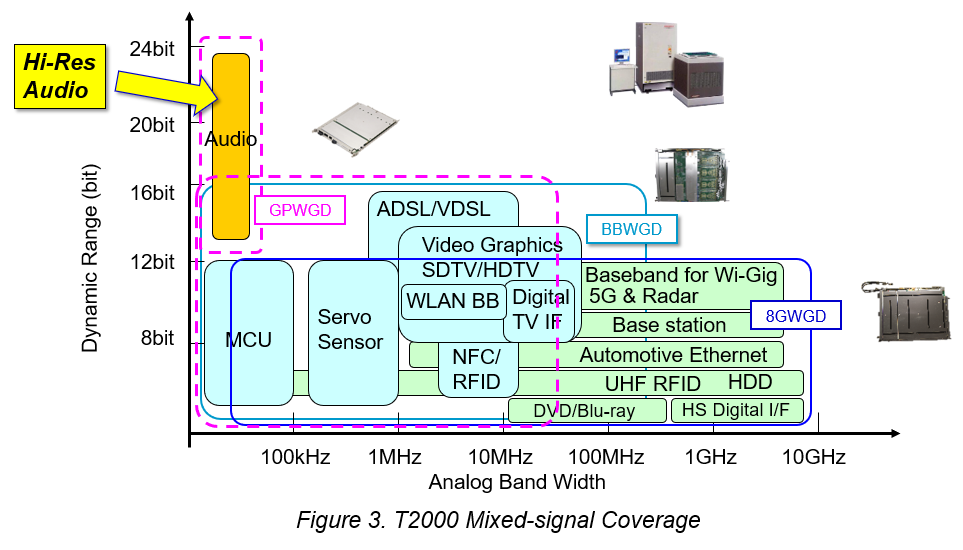

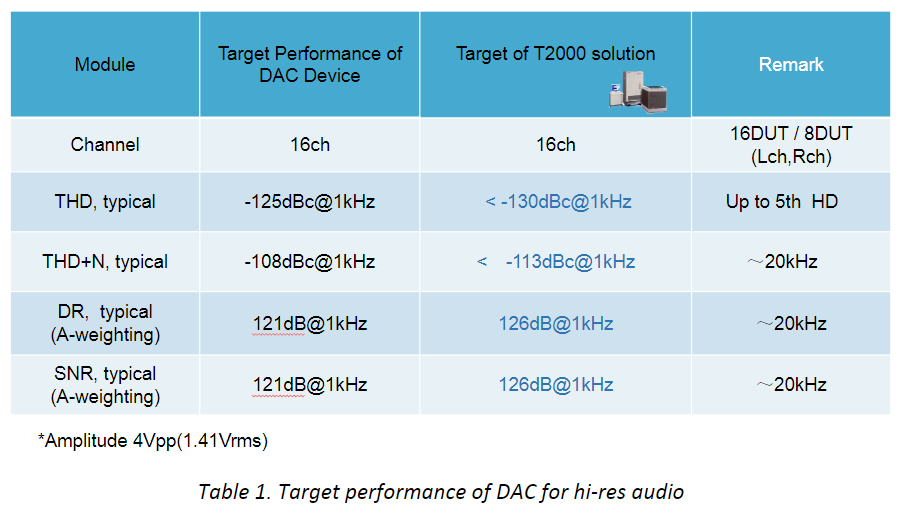

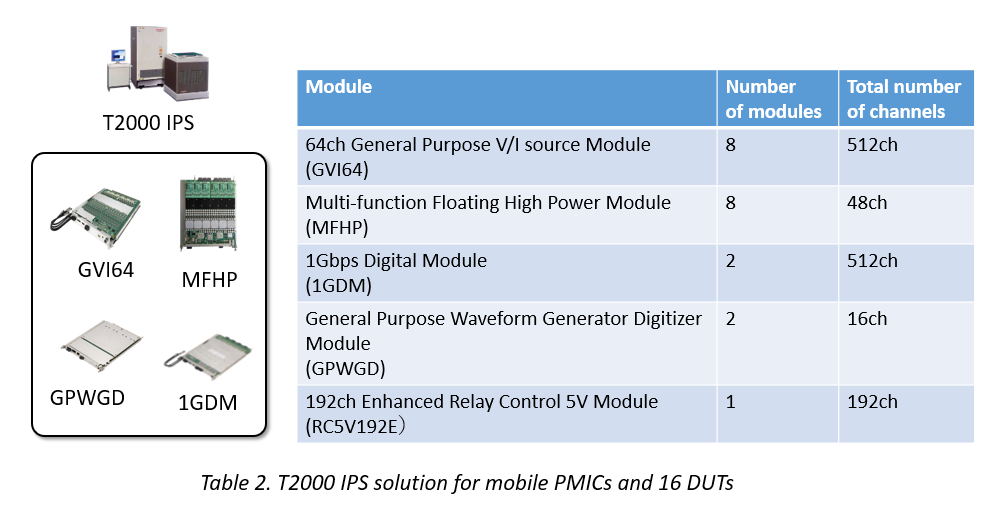

Among the products that Advantest will feature in booth #2044 in Hall 2 are eight new systems and enhancements that the company has announced within the past year. These include three new members of the B6700 product family of burn-in memory testers – models B6700D -S and -L – designed to boost parallel testing capacity and lower the cost of test for NAND flash devices; the newest additions to the MPT3000 platform that make it the industry’s first fully integrated test solution for developing, debugging and mass producing PCIe Gen 4 solid-state drives (SSD); the FVI16 floating power VI source that extends the V93000 platform’s capabilities to include testing of advanced ICs for automotive, industrial and PMIC applications; the new T5503HS2 system, the only tester of its kind to evaluate the advanced features of next-generation, high-speed LPDDR5 and DDR5 memory ICs; and two new modules – the multifunction mixed high voltage (MMXHE) and multifunction floating high power (MFHPE) units – that enable systems in the established T2000 series to more efficiently test devices used in the power trains of electric vehicles.

The booth will include an automotive display to help show attendees visualize how and where Advantest’s equipment is being applied to improve the performance and reliability of on-board electronics, from LIDAR systems to mobile communications.

Other products on display will be the flexible T5851 memory tester for next-generation mobile protocol NAND such as UFS3.x and PCIe Gen4 BGA; the T6391 system for testing LCD drivers; the EVA100 measurement system, which has a new HVI (high-voltage VI source and measurement) module that extends the platform’s range to include high-power ICs used in large-volume consumer applications; the portable, remotely operable M4171 handler, capable of automated device loading and unloading as well as active thermal control (ATC); the E3650, a new high-end model of MVM-SEM enabling next-generation photomasks; the F7000 e-beam lithography tool for the 1X-nm technology node; and probe cards optimized for use in Advantest’s testers.

Company experts will be on site to answer attendees’ questions about the latest test technologies and best practices.

Sponsorships

In addition to exhibiting, Advantest is a gold sponsor of this year’s SEMICON Japan. This includes sponsorship of the Presidents Reception networking event on the evening of December 12 and the SEMI Technology Symposium (STS) on “Challenges to Test Diversity” to be held at TechStage South on December 14.

Advantest also is the sole sponsor of the inaugural SMART Transportation Summit in reception hall A in the Conference Tower on December 13. Judy Davies, Advantest’s vice president of global marketing communications, will present the inaugural address for the Summit, at which automotive manufacturers will discuss technology advances and business prospects associated with smart and electrified vehicles.

The four-hour event will open with a session in which automotive industry executives from Toyota’s Info Technology Center, Volkswagen and Honda’s R&D organization will share their perspectives on the future of automated driving, electrified vehicles and connected cars. Following a luncheon, the program’s second session will feature semiconductor industry representatives from Denso, Bosch and Infineon discussing innovations in transportation systems and what the future may hold for both business and technology.

Read More

By GO SEMI & Beyond staff

By GO SEMI & Beyond staff