CREA Brings Power Semiconductor Know-how to Advantest

By GO SEMI & Beyond staff

In June 2022, Advantest announced its acquisition of Italian ATE company CREA. As leading developer and provider of equipment for testing power semiconductors, CREA brings vital capabilities to Advantest’s portfolio of test solutions. To delve further into the acquisition and how it will benefit Advantest’s customers, we talked with Fabio Marino, director of Advantest’s Power, Analog and Controller Business.

Q: What prompted Advantest to pursue adding power semiconductor test to its capabilities?

A. When considering any strategic action, we are guided by our Grand Design, which defines the commitments and strategies needed to further our goal of enabling leading-edge technologies by adding customer value throughout the semiconductor value chain. This goes hand in hand with looking at relevant market and technology advancements.

Until recently, the high-voltage power device market was a niche, low-volume market. However, fast-growing adoption of electric vehicles (EVs) is driving heightened demand for discrete components. Demand for power semiconductors is growing significantly in response to the need to utilize power more efficiently for EV applications – we expect the market for these devices to grow by 10x over the next eight years. As a result, we realized we would need to pursue this market by bringing power semiconductor test into our portfolio.

Q. Why was CREA selected for acquisition?

A. While there are several suppliers of power semiconductor testers, we determined that CREA was the best fit for Advantest because of several factors, including its:

- Superior technology platform, which covers both static and dynamic power test, proven over 30 years;

- Expertise in compound semiconductors, including silicon carbide (SiC) and gallium nitride (GaN);

- Strong installed base, with more than 200 testers installed at semiconductor makers worldwide; and

- Synergistic business approach, viewing customers as partners, with the goal of full solutions and support for customers’ testing needs.

Q. How is CREA being integrated into Advantest?

A. CREA will remain headquartered in Italy as a wholly owned subsidiary of Advantest Europe, within our ATE Business Group. CREA’s management team is continuing to run the subsidiary, with Advantest providing additional team support as needed.

Q. Can you talk about the company’s portfolio a bit? What makes it such a strong addition to Advantest’s offerings?

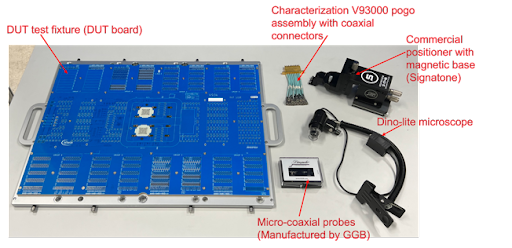

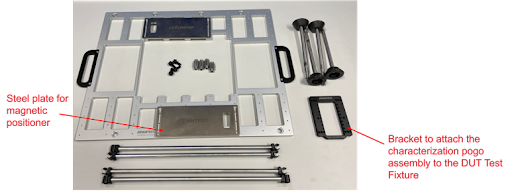

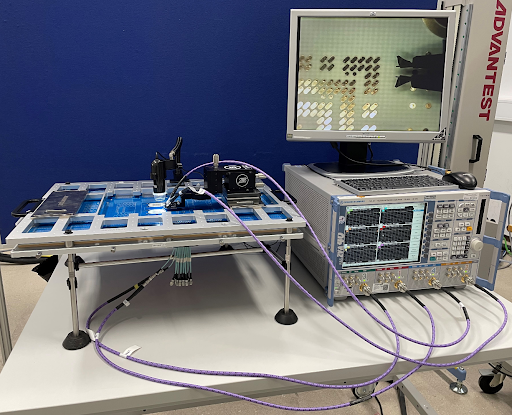

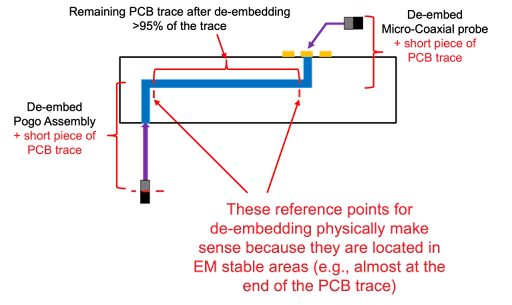

A. CREA’s proprietary technologies are key to its power device test capabilities. These include its PCI probe card interface, vital for known good die (KGD) and wafer test; LSI low stray inductance technology, essential to reduce parasite effects during test; and RTH remote test head, which works in conjunction with LSI to achieve high performance up to 1.5m away from the tester to enable handler and wafer prober use for mass production.

These products are integrated into CREA’s tester line, which comprises three product families:

- The MT100 family, with a range of voltages and currents, which covers test requirements for static parameters from dies to complex configuration modules;

- The MT200 family, which adds dynamic and combined parameter test to reach ranges up to 10 kV and 10 kA; and

- The MT300 family, designed to satisfy the market’s most stringent requirements.

The CREA portfolio also includes turnkey solutions incorporating its fixture system, as well as manual and automated handlers.

Q. How do customers view the acquisition?

A. Customer reaction has been very positive. CREA has developed an excellent reputation over its 30 years of existence, and customers understand the strengths their test systems bring to Advantest and how they benefit in return. CREA will retain, to a large extent, the fast response time and flexibility it enjoyed as a standalone company, while, as a subsidiary of Advantest, its development team will have access to our broad corporate resources and collective knowledge base, which will benefit their ongoing technology advancement efforts. We’re excited by the opportunities the CREA acquisition provides for increasing customer value by enabling us to jointly develop new solutions to meet customers’ future demands.

In addition, by integrating CREA’s product lineups, development capabilities, customer base, and outstanding technical team into Advantest, we’ll be able to expand our solutions for power semiconductors. This will benefit both our company and our customers by allowing us to directly contribute to the broad goal of realizing a Net-Zero society.

Q. What’s the bottom line for Advantest with this acquisition?

A. We intend to be a key player in the high-power market, and we believe that the technology CREA brings to the table will give us a competitive advantage, allowing us to have a significant market share. Moreover, CREA’s synergy with our established customer relations and global account setup will combine to help drive sales for these power semiconductor test products.

Read More