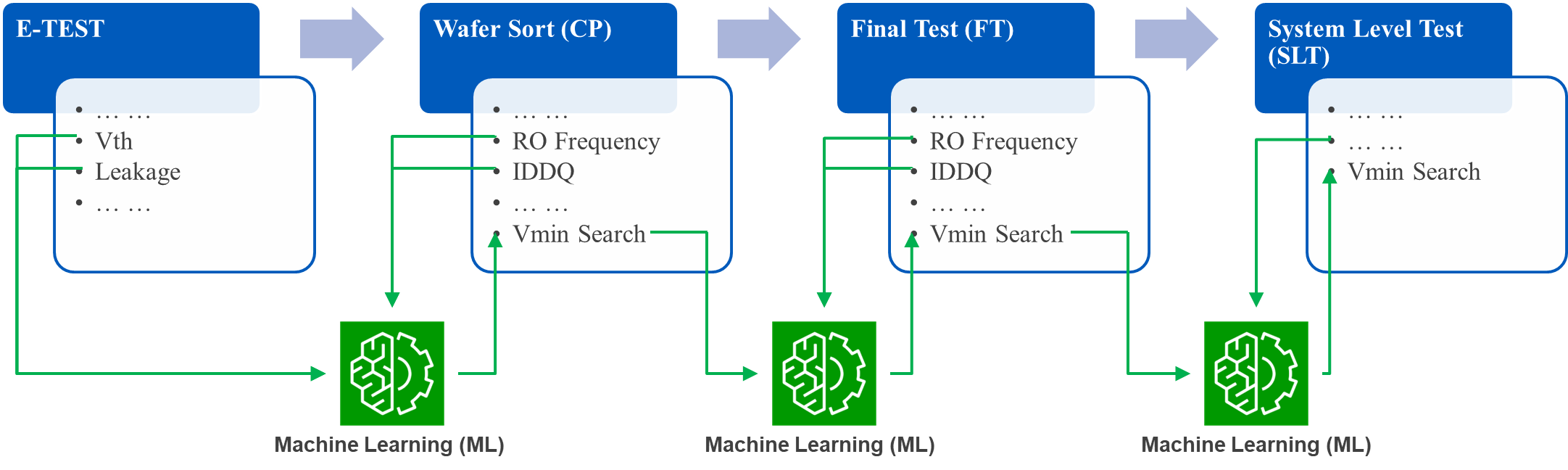

Singulated Die Test Ensures Stacked Die Quality as Power Density Rises

The accelerating rate at which the industry adopts new process nodes is posing critical test challenges. Shrinking geometries combined with increased design complexity are leading to ever higher levels of power density, driving the need for singulated die test (SDT) with active thermal control.

Read More